Publication # 24707 Revision: 3.08 Issue Date: September 2003 © 2002, 2003 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel, or otherwise, to any intellectual property rights are granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD Arrow logo, AMD Athlon, AMD Opteron, and combinations thereof, and the AMD64 logo, are trademarks of Advanced Micro Devices, Inc.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# Contents

| Revision | History                                                    | 3  |

|----------|------------------------------------------------------------|----|

| Chapter  | 1 Description                                              | 5  |

| 1.1      | Specification Overview                                     | 5  |

| 1.2      | Pin-Strapped Configuration                                 | 5  |

| 1.3      | Processor Frequency Selection and Spread Spectrum Clocking | 5  |

| 1.3.1    | Reserved Test Mode Operating States                        | 6  |

| 1.4      | Differential Push-Pull Processor Clock Outputs             | 6  |

| 1.5      | Selectable 33-MHz or 66-MHz Clock Outputs                  | 6  |

| 1.6      | PCISTOP33_L Control Signal                                 | 6  |

| 1.6.1    | Starting the 33-MHz PCI Clocks                             | 6  |

| 1.6.2    | 2 Stopping the 33-MHz PCI Clocks                           | 7  |

| 1.7      | Input Reference Crystal Definition                         | 8  |

| 1.8      | Internal Input Pullup Resistors                            | 8  |

| 1.9      | Software Interface and Control                             | 8  |

| 1.9.1    | Hardware Selection with Software Programmable Overrides    | 8  |

| 1.9.2    | 2 Configuration Read-Back                                  | 8  |

| Chapter  | 2 Features                                                 | 9  |

| Chapter  | 3 Frequency Selections                                     | 11 |

| Chapter  | 4 Logic Block Diagram                                      | 17 |

| Chapter  | 5 Pin Locations and Descriptions                           |    |

| Chapter  | 6 Package Pinout – 48-Pin SSOP                             | 23 |

| Chapter  | 7 Electrical Specifications                                | 25 |

| 7.1      | Absolute Maximum Ratings                                   | 25 |

| 7.2      | Operating Conditions                                       | 25 |

| 7.3      | Electrical Characteristics                                 | 26 |

| 7.3.1    | Logic Inputs                                               |    |

| 7.3.2    | 2 SDATA, SCLK Input/Output                                 |    |

###

| Clock ( | Gener | ator Specification for AMD64 Processors 247          | 07   | Rev. 3.08 | September 2003 |

|---------|-------|------------------------------------------------------|------|-----------|----------------|

| 7.3.    | .3    | X1, X2 Crystal Input/Feedback                        |      |           |                |

| 7.3.    | .4    | PCI/ HyperTransport <sup>TM</sup> Clock Outputs      |      |           |                |

| 7.3.    | .5    | REF[2:0] Clock Outputs                               |      |           |                |

| 7.3.    | .6    | USB, 24_48MHz Clock Outputs                          |      |           |                |

| 7.3.    | .7    | CPUT[1:0], CPUC[1:0] Clock Outputs                   |      |           |                |

| 7.3.    | .8    | cheme                                                |      |           |                |

| 7.3.    | .9    | Differential Processor Clock Input                   |      |           |                |

| 7.3.    | .10   | Differential Processor Clock for AMD64 Processors Te | est  | Load      |                |

| 7.4     | Spre  | ead Spectrum                                         |      |           |                |

| 7.5     | Ske   | W                                                    |      |           |                |

| Chapter | r 8   | SMBus Interface                                      | •••• | •••••     |                |

| 8.1     | SM    | Bus Protocol                                         |      |           |                |

| 8.1.    | .1    | Block Write                                          |      |           |                |

| 8.1.    | .2    | Block Read                                           |      |           |                |

# **List of Figures**

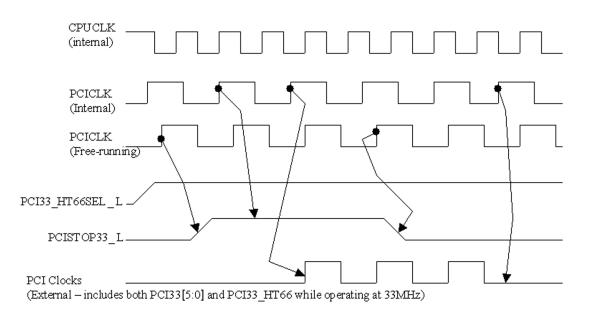

| Figure 1. PCISTOP33_L Control Signal                                  | 7  |

|-----------------------------------------------------------------------|----|

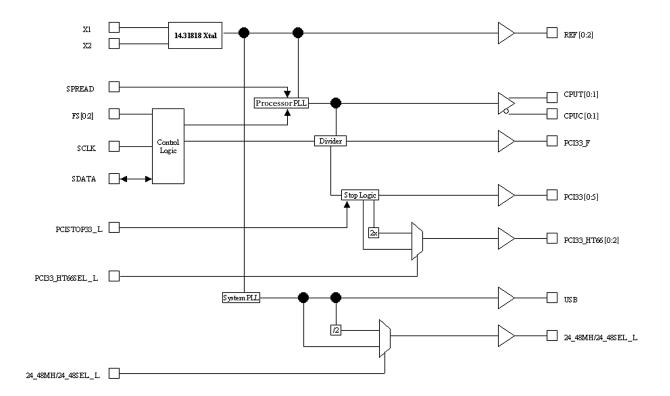

| Figure 2. Processor Clock Logic Block Diagram                         | 17 |

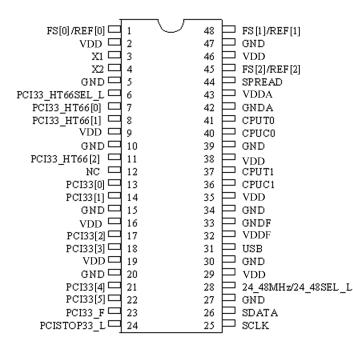

| Figure 3. SSOP Package Pinout                                         | 23 |

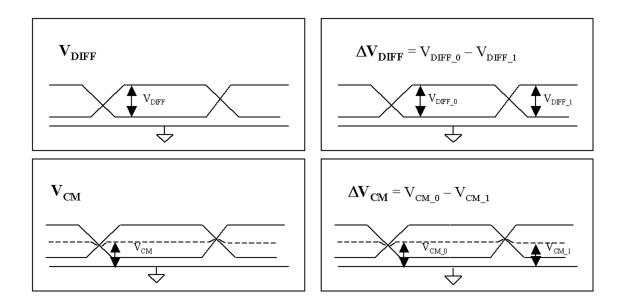

| Figure 4. Single-Ended Measurement Definitions                        | 33 |

| Figure 5. Four-Layer Motherboard Stack-Up and Impedance               | 34 |

| Figure 6. Motherboard Processor Clock Termination Scheme              | 35 |

| Figure 7. Target Processor Internal Bias Generation                   | 36 |

| Figure 8. Differential Processor Clock for AMD64 Processors Test Load | 37 |

##

Clock Generator Specification for AMD64 Processors

# **List of Tables**

| Table 1. System Clock Features                                                                                          | 9  |

|-------------------------------------------------------------------------------------------------------------------------|----|

| Table 2. Frequency Selections                                                                                           | 11 |

| Table 3. Pin Locations and Descriptions                                                                                 |    |

| Table 4. Absolute Maximum Ratings                                                                                       |    |

| Table 5. Operating Conditions                                                                                           |    |

| Table 6. Logic Input Electrical Characteristics                                                                         |    |

| Table 7. SDATA and SCLK Input Electrical Characteristics *                                                              |    |

| Table 8. Crystal Input/Feedback Electrical Characteristics                                                              |    |

| Table 9. PCI/HyperTransport <sup>™</sup> Clock Output Electrical Characteristics<br>(Lump Capacitance Test Load =30 pF) |    |

| Table 10. Reference Clock Output Electrical Characteristics<br>(Lump Capacitance Test Load = 20 pF)                     |    |

| Table 11. 24_48 MHz, USB Clock Output Electrical Characteristics<br>(Lump Capacitance Test Load = 20 pF)                |    |

| Table 12. Processor Clock Output Electrical Characteristics                                                             |    |

| Table 13. Board Stack-Up Parameters                                                                                     |    |

| Table 14. Spread Spectrum Characteristics                                                                               |    |

| Table 15. Skew Characteristics                                                                                          |    |

| Table 16. I <sup>2</sup> C Address                                                                                      |    |

| Table 17. Byte0: Frequency and Spread Spectrum Control Register                                                         |    |

| Table 18. Byte1: PCI Clock Control Register (1=Enabled, 0=Disabled)                                                     |    |

| Table 19. Byte2: PCI Clock, USB, 24_48MHz, REF[2:0] Control Register<br>(1=Enabled, 0=Disabled)                         |    |

| Table 20. Byte3: PCI Clock Free Running Select Control Register                                                         |    |

| Table 21. Byte4: Pin Latched/Real Time State (and One Free Running Control)                                             |    |

| Table 22. Byte5: Clock Vendor ID                                                                                        |    |

| Table 23. Byte6: Reserved for Byte Count                                                                                |    |

# **Revision History**

| Date           | Revision | Changes                                                                                                                                                                                                             |

|----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| September 2003 | 3.08     | Fourth Public release.                                                                                                                                                                                              |

| September 2003 | 3.07     | Changed the title of the document to "Clock Generator Specification for AMD64 Processors" and changed references throughout the document.                                                                           |

| November 2002  | 3.06     | Third Public release.                                                                                                                                                                                               |

| November 2002  | 3.05     | Added note in Table 2 for resistor strapping recommendation.<br>Made changes in Table 3 for pin descriptions section of FS(2:0) signals.                                                                            |

| November 2002  | 3.04     | Changed the title of the document to "Clock Generator Specification for AMD Athlon <sup>TM</sup> 64 and AMD Opteron <sup>TM</sup> Processors" and changed references throughout the document.                       |

| September 2002 | 3.03     | Second Public release.                                                                                                                                                                                              |

| September 2002 | 3.02     | Internal revision.                                                                                                                                                                                                  |

| August 2002    | 3.01     | Changed the title of the document to "Clock Generator Specification for AMD Athlon <sup>™</sup> and AMD Opteron <sup>™</sup> Processors Based on Hammer Technology" and changed references throughout the document. |

| August 2002    | 3.00     | Initial Public release.                                                                                                                                                                                             |

##

Clock Generator Specification for AMD64 Processors

# Chapter 1 Description

This specification is intended to provide a definition of the minimum set of requirements for the first AMD64 processors system clock generators.

## **1.1 Specification Overview**

The goal of this specification is

- to provide enough information to enable development of clock generators for the AMD64 processors

- to provide the definition of a minimum feature set for a clock generator that enables initial platform shipments

- to allow clock generator vendors the flexibility to provide product differentiation above and beyond this minimum feature set

- to provide backward compatibility with AMD Athlon<sup>™</sup> processor-based platforms

## **1.2 Pin-Strapped Configuration**

Upon power up, the device samples the input states of various configuration input pins to define the correct operating state without the need for software configuration through the  $I^2C$  interface. The  $I^2C$  interface to internal configuration registers provides a method to optimize the operating state of the clock generator.

*Note*: Changes made through the  $I^2C$  interface will override the hardware pin strapped configuration.

## 1.3 Processor Frequency Selection and Spread Spectrum Clocking

Processor frequency selection of 100, 133, 166, and 200 MHz are defined from hardware-sampled inputs. Additional frequencies and operating states (combinations of processor frequency and spread spectrum clocking features) can be selected through the I<sup>2</sup>C programmable interface. The specified features in this specification provide a minimum set for AMD64 processor-based platforms. Additional features may be provided at the discretion of the clock generator manufacturer.

Spread spectrum modulation (down-spread only) is required for all outputs derived from the internal processor PLL as shown in Figure 1 on page 7. This includes the processor, PCI33 and PCI33\_HT66 outputs. The REF, USB, and 24\_48 MHz clocks are not affected by spread spectrum control. The spread spectrum requirements include the ability to enable and disable 0.5% down spread clocking. A 0.5% down spread, 33-kHz triangular modulation is required and

other spread amounts less than 0.5% down spread and less than 50 kHz  $\Delta f/\Delta t$  modulation are left to the clock generator vendor to include as differentiating features.

### **1.3.1** Reserved Test Mode Operating States

This specification defines two test modes and reserves one other for the purpose of providing required system debug and system test operating modes. The reserved manufacturer test mode is provided for each clock vendor to implement an operating mode specific to their own production test flow needs and is not required for system operation.

# 1.4 Differential Push-Pull Processor Clock Outputs

This clock generator is specified to provide push-pull driver type differential outputs for the processor clocks (2-pair) instead of the common open drain style used for AMD Athlon processorbased platforms. This provides a more testable product and results in less variation in edge rate and differential skew as seen by the processor. The processor clock termination scheme has been derived such that 15–55 ohm, 3.3-V output drivers can be used for the processor clocks.

# 1.5 Selectable 33-MHz or 66-MHz Clock Outputs

This clock generator specification defines a number of clock outputs that are selectable between 33 MHz and 66 MHz. This selection provides flexibility across platforms that may implement a combination of 33-MHz PCI resources, 66-MHz PCI resources, and HyperTransport<sup>™</sup> technology resources.

*Note:* HyperTransport technology is the HyperTransport Technology Consortium's next generation interconnect technology that is designed for use with all AMD64 platforms.

# 1.6 PCISTOP33\_L Control Signal

This clock generator specification defines one asynchronous PCISTOP33\_L signal that provides control for 33-MHz output clocks. Both the PCI33 and PCI33\_HT66 clocks, while operating at 33MHz, must stop in response to PCISTOP33\_L assertions. While operating at 66 MHz, the PCI33\_HT66 outputs are not affected by PCISTOP33\_L assertions.

The 33-MHz PCI clock outputs, once stopped, should be in the Low state and started with a full high-pulse width specified. The 33-MHz PCI clock outputs on latency cycles are only one rising PCI clock turned off. Latency is one PCI clock. Section 1.6.1 and Section 1.6.2 on page 7, along with Figure 1 on page 7 gives a description and timing diagram respectively, of the required timing sequence:

### 1.6.1 Starting the 33-MHz PCI Clocks

The 33MHz PCI clocks must be started using the following sequence of events:

24707 Rev. 3.08 September 2003

- 1. On a given PCI clock rising edge, the PCISTOP33\_L signal is asserted (first arrow from the left in the timing diagram).

- 2. On the next rising edge of the PCI clock, the clock synthesis chip samples PCIST0P33\_L deasserted (second arrow from the left).

- 3. The PCI clocks start running with the next rising edge of the PCI clock (third arrow from the left).

### 1.6.2 Stopping the 33-MHz PCI Clocks

The 33-MHz PCI clocks must be stopped using the following sequence of events:

- 1. On a rising edge of the PCI clock, the PCISTOP33\_L signal is asserted (4th arrow).

- 2. On the next rising edge of the PCI clock, the clock synthesis chip samples PCISTOP33\_L asserted.

- 3. On the next falling edge of the PCI clock, the PCI clocks go Low and stay Low.

Figure 1 is a picture of the PCISTOP33\_L control sequence. All numbered arrow references are counted from left to right.

#### Figure 1. PCISTOP33\_L Control Signal

Note: The fifth arrow, from the left, shows there is no rising edge on the stopped PCI clocks.

The following notes give additional information on the PCISTOP33\_L control sequence.

Notes:

- 1. All timing is referenced to internal CPUCLK.

- 2. PCISTOP33\_L is an asynchronous input.

- *3. All other clocks continue to run undisturbed.*

- *4. PCI33\_HT66SEL\_L* is shown in the High state.

- 5. PCISTOP33\_L must meet 10 ns setup/hold times.

# **1.7 Input Reference Crystal Definition**

The crystal inputs and pin loading should be compatible with 18-pF crystals.

# **1.8 Internal Input Pullup Resistors**

This specification defines internal pullup resistors on most of the control inputs. The internal input pullup resistors allow the input pins to be left unconnected in applications where their function is unnecessary. Additionally, these input pullup resistors provide the required pullup for open drain-type outputs for SMBus. The general range of values is provided for these internal pullups.

# **1.9** Software Interface and Control

Software interface and control of the clock generator are described in Sections 1.9.1 and 1.9.2.

### 1.9.1 Hardware Selection with Software Programmable Overrides

Configuration of the features of the clock generator can be completed through hardware pin strapping alone or by hardware pin strapping with optimization of features through programmable registers accessed through the SMBus interface. The values of the programmable registers will override any hardware strapped settings, once the settings are changed.

## 1.9.2 Configuration Read-Back

The values of the programmable registers can be read back through the SMBus interface to allow the current operating state of the device to be determined.

# Chapter 2 Features

This specification describes the main clock generator for AMD64 platforms. Table 1 describes the system clock features.

Table 1. System Clock Features

| Features                               | Frequency                                | Туре                      | Voltage |

|----------------------------------------|------------------------------------------|---------------------------|---------|

| Two differential pair processor clocks | 200-MHz, 166MHz, 133-<br>MHz, or 100-MHz | Differential<br>push-pull | 3.3 V   |

| Six PCI clocks                         | 33-MHz                                   | Push-pull                 | 3.3 V   |

| One free running PCI clock             | 33-MHz                                   | Push-pull                 | 3.3 V   |

| Three AGP/HT clocks                    | 33-MHz or 66 MHz                         | Push-pull                 | 3.3 V   |

| USBCLK                                 | 48-MHz                                   | Push-pull                 | 3.3 V   |

| FDC clock                              | 24-MHz or 48MHz                          | Push-pull                 | 3.3 V   |

| Three Reference clocks                 | 14.318-MHz                               | Push-pull                 | 3.3 V   |

Additional features of the system clock are as follows:

- 3.3-V operation

- Two true differential processor clocks pairs (supports both 1P and 2P platforms)

- Seven 3.3-V dedicated 33-MHz PCI clocks, one free-running

- Three 3.3-V selectable 66-MHz or 33 MHz clocks to be used for HyperTransport<sup>™</sup> technology reference clocks or PCI 33-MHz clocks

- One 3.3-V 48-MHz output for USB

- One 3.3-V 24-MHz or 48-MHz for SIO

- Three 3.3-V 14.318-MHz reference clocks (one additional to provide reference to external 24.576 MHz generator if needed for AC97 codecs)

- EMI Suppression using spread spectrum technology (down spread only with 33 kHz triangular modulation)

- SMbus interface for configuration register programming and read back (Rev 1.0)

- Power management control inputs

- A 48-pin SSOP

##

Clock Generator Specification for AMD64 Processors

# Chapter 3 Frequency Selections

This chapter contains frequency selections for the Clock Generator and they are shown in Table 2.

| Table 2. | Frequency | Selections |

|----------|-----------|------------|

|----------|-----------|------------|

| Input Configuration |     |     |                     |                 |            |     | PCI33 (MHz) | PCI33_HT66<br>(MHz) | 24_48<br>(MHz) | 14.318<br>(MHz) | Comment                                |

|---------------------|-----|-----|---------------------|-----------------|------------|-----|-------------|---------------------|----------------|-----------------|----------------------------------------|

| FS2                 | FS1 | FS0 | PCI33_HT66<br>SEL_L | PCI<br>STOP33_L | 24_48SEL_L |     |             |                     |                |                 |                                        |

| 1                   | 1   | 1   | Х                   | 1               | Х          | 200 | 33          | 33<br>or<br>66      | 24 or<br>48    | 14.318          | Normal<br>AMD64 Processor<br>Operation |

| 1                   | 1   | 0   | Х                   | 1               | Х          | 166 | 33          | 33<br>or<br>66      | 24 or<br>48    | 14.318          | Reserved                               |

Notes:

1. During bypass mode the X1 input pin can be driven with an external clock signal from 10 MHz to 100 MHz. This mode is used in system debug for frequency testing and is planned to be used in the smart burn-in systems for the AMD64 processors used for production burn-in capability.

2. These operating modes are reserved for vendor specific test requirements and may be different from vendor to vendor. These modes will not be used in the system.

3. In these cases, FS[2:0] is not equal to 000b or 001b.

4. It is highly recommended to connect an external pullup resistor and pull down resistor on signals FS[2:0] and 24\_48SEL\_L to ensure that these signals achieve the desired logic level and to determine the correct frequency selection under various loading and part leakage conditions. The value for the external pull up resistor should be 10 k ohm and the value for the external pull down resistor should be 1K ohm.

24707 Rev. 3.08 September 2003

|     |     | Input | Configu             | iration         |            | Processor<br>(MHz)        | PCI33 (MHz)          | PCI33_HT66<br>(MHz)  | 24_48<br>(MHz) | 14.318<br>(MHz) | Comment                                                   |

|-----|-----|-------|---------------------|-----------------|------------|---------------------------|----------------------|----------------------|----------------|-----------------|-----------------------------------------------------------|

| FS2 | FS1 | FS0   | PCI33_HT66<br>SEL_L | PCI<br>STOP33_L | 24_48SEL_L |                           |                      |                      |                |                 |                                                           |

| 1   | 0   | 1     | Х                   | 1               | Х          | 133                       | 33                   | 33 or<br>66          | 24 or<br>48    | 14.318          | AMD Athlon <sup>™</sup><br>processor<br>compatible        |

| 14  | 0   | 0     | Х                   | 1               | Х          | 100                       | 33                   | 33 or<br>66          | 24 or<br>48    | 14.318          | AMD Athlon<br>processor<br>compatible                     |

| 0   | 1   | 1     | Х                   | 1               | Х          |                           |                      |                      |                |                 | Reserved <sup>2</sup>                                     |

| 0   | 1   | 0     | Х                   | 1               | Х          | _                         |                      |                      | _              |                 | Reserved <sup>2</sup>                                     |

| 0   | 0   | 1     | 1                   | 1               | Х          | X1<br>input<br>(pin3<br>) | =X1 /<br>6<br>(pin3) | =X1 /<br>6<br>(pin3) | 0              | 0               | Bypass mode<br>for bring up and<br>mfgr test <sup>1</sup> |

| 0   | 0   | 1     | 0                   | 1               | Х          | X1<br>input               | =X1 /<br>6           | =X1 / 3              | 0              | 0               | Bypass mode<br>for bring up and<br>mfgr test <sup>1</sup> |

Notes:

1. During bypass mode the X1 input pin can be driven with an external clock signal from 10 MHz to 100 MHz. This mode is used in system debug for frequency testing and is planned to be used in the smart burn-in systems for the AMD64 processors used for production burn-in capability.

- 2. These operating modes are reserved for vendor specific test requirements and may be different from vendor to vendor. These modes will not be used in the system.

- 3. In these cases, FS[2:0] is not equal to 000b or 001b.

- 4. It is highly recommended to connect an external pullup resistor and pull down resistor on signals FS[2:0] and 24\_48SEL\_L to ensure that these signals achieve the desired logic level and to determine the correct frequency selection under various loading and part leakage conditions. The value for the external pull up resistor should be 10 k ohm and the value for the external pull down resistor should be 1K ohm.

|      |     |                        | ť                                      | ``                     | Jitiliucu                           | ,<br>                         |                         |                          | 1                      |                               |                                                                 |

|------|-----|------------------------|----------------------------------------|------------------------|-------------------------------------|-------------------------------|-------------------------|--------------------------|------------------------|-------------------------------|-----------------------------------------------------------------|

|      |     | Input                  | : Configu                              | iration                |                                     | Processor<br>(MHz)            | PCI33 (MHz)             | PCI33_HT66<br>(MHz)      | 24_48<br>(MHz)         | 14.318<br>(MHz)               | Comment                                                         |

| FS2  | FS1 | FS0                    | PCI33_HT66<br>SEL_L                    | PCI<br>STOP33_L        | 24_48SEL_L                          |                               |                         |                          |                        |                               |                                                                 |

| 0    | 0   | 0                      | Х                                      | 1                      | Х                                   | Hi-Z                          | Hi-Z                    | Hi-Z                     | Hi-Z                   | Hi-Z                          | Tri-state mode<br>for board level<br>test                       |

| X    | Х   | Х                      | 0                                      | 1                      | Х                                   | 100,<br>133,<br>166 or<br>200 | 33                      | 66                       | 24 or<br>48            | 14.318                        | 33 MHz vs. 66<br>MHz output<br>select <sup>3</sup>              |

| X    | Х   | Х                      | 1                                      | 1                      | Х                                   | 100,133<br>, 166, or<br>200   | 33                      | 33                       | 24 or<br>48            | 14.318                        | 33 MHz vs. 66<br>MHz output<br>select <sup>3</sup>              |

| Note | s:  |                        |                                        |                        |                                     |                               |                         |                          |                        |                               |                                                                 |

|      | 1.  | 100                    | MHz. Th                                | is mode is             | used in s                           | system debu                   | ig for free             | quency tes               | sting and i            |                               | om 10 MHz to<br>o be used in the<br>oility.                     |

|      | 2.  |                        | ·                                      | 0                      |                                     | ved for ven<br>will not be    | · ·                     | ·                        | quirement              | ts and may l                  | be different from                                               |

|      | 3.  | In th                  | ese cases                              | s, FS[2:0]             | is not eq                           | ual to 000b                   | or 001b.                |                          |                        |                               |                                                                 |

|      | 4.  | FS[2<br>deter<br>value | 2:0] and 2<br>rmine the<br>e for the c | 24_48SEL<br>correct fi | _L to en.<br>requency<br>ull up res | sure that the selection u     | ese signa<br>Inder vari | ls achieve<br>ious loadi | the desir<br>ng and pa | ed logic lev<br>art leakage c | tor on signals<br>el and to<br>conditions. The<br>mal pull down |

#### Table 2. Frequency Selections (Continued)

24707 Rev. 3.08 September 2003

| Input Configuration |     |                |                     |                 |            | Processor<br>(MHz)             | PCI33 (MHz) | PCI33_HT66<br>(MHz) | 24_48<br>(MHz) | 14.318<br>(MHz) | Comment                                                     |

|---------------------|-----|----------------|---------------------|-----------------|------------|--------------------------------|-------------|---------------------|----------------|-----------------|-------------------------------------------------------------|

| FS2                 | FS1 | $\mathbf{FS0}$ | PCI33_HT66<br>SEL_L | PCI<br>STOP33_L | 24_48SEL_L |                                |             |                     |                |                 |                                                             |

| X                   | X   | X              | Х                   | 1               | 1          | 100,<br>133,<br>166 or<br>200  | 33          | 33 or<br>66         | 24             | 14.318          | 24 vs. 48 MHz<br>output select <sup>3</sup>                 |

| X                   | X   | X              | Х                   | 1               | 0          | 100,<br>133,<br>166, or<br>200 | 33          | 33 or<br>66         | 48             | 14.318          | 24 vs. 48 MHz<br>output select <sup>3</sup>                 |

| X                   | Х   | Х              | 0                   | 0               | Х          | 100,<br>133,<br>166,<br>200    | 0           | 66                  | 24 or<br>48    | 14.318          | PCISTOP vs.<br>33 MHz and<br>66 MHz<br>selects <sup>3</sup> |

#### **Table 2. Frequency Selections (Continued)**

Notes:

1. During bypass mode the X1 input pin can be driven with an external clock signal from 10 MHz to 100 MHz. This mode is used in system debug for frequency testing and is planned to be used in the smart burn-in systems for the AMD64 processors used for production burn-in capability.

2. These operating modes are reserved for vendor specific test requirements and may be different from vendor to vendor. These modes will not be used in the system.

3. In these cases, FS[2:0] is not equal to 000b or 001b.

4. It is highly recommended to connect an external pullup resistor and pull down resistor on signals FS[2:0] and 24\_48SEL\_L to ensure that these signals achieve the desired logic level and to determine the correct frequency selection under various loading and part leakage conditions. The value for the external pull up resistor should be 10 k ohm and the value for the external pull down resistor should be 1K ohm.

| Input Configuration |     |     |                     | Processor<br>(MHz) | PCI33 (MHz) | PCI33_HT66<br>(MHz)         | 24_48<br>(MHz) | 14.318<br>(MHz) | Comment     |        |                                                             |

|---------------------|-----|-----|---------------------|--------------------|-------------|-----------------------------|----------------|-----------------|-------------|--------|-------------------------------------------------------------|

| FS2                 | FS1 | FS0 | PCI33_HT66<br>SEL_L | PCI<br>STOP33_L    | 24_48SEL_L  |                             |                |                 |             |        |                                                             |

| X                   | X   | X   | 0                   | 1                  | Х           | 100,<br>133,<br>166,<br>200 | 33             | 66              | 24 or<br>48 | 14.318 | PCISTOP vs.<br>33 MHz and<br>66 MHz<br>selects <sup>3</sup> |

| X                   | X   | X   | 1                   | 0                  | Х           | 100,<br>133,<br>166,<br>200 | 0              | 0               | 24 or<br>48 | 14.318 | PCISTOP vs.<br>33 MHz and<br>66 MHz<br>selects <sup>3</sup> |

| X                   | Х   | Х   | 1                   | 1                  | Х           | 100.<br>133,<br>166,<br>200 | 33             | 33              | 24 or<br>48 | 14/318 | PCISTOP vs.<br>33 MHz and<br>66 MHz<br>selects <sup>3</sup> |

#### **Table 2. Frequency Selections (Continued)**

Notes:

1. During bypass mode the X1 input pin can be driven with an external clock signal from 10 MHz to 100 MHz. This mode is used in system debug for frequency testing and is planned to be used in the smart burn-in systems for the AMD64 processors used for production burn-in capability.

2. These operating modes are reserved for vendor specific test requirements and may be different from vendor to vendor. These modes will not be used in the system.

3. In these cases, FS[2:0] is not equal to 000b or 001b.

**4.** It is highly recommended to connect an external pullup resistor and pull down resistor on signals *FS*[2:0] and 24\_48SEL\_L to ensure that these signals achieve the desired logic level and to determine the correct frequency selection under various loading and part leakage conditions. The value for the external pull up resistor should be 10 k ohm and the value for the external pull down resistor should be 1K ohm.

##

Clock Generator Specification for AMD64 Processors

# Chapter 4 Logic Block Diagram

This chapter and Figure 2 illustrate the processor clock logic.

Figure 2. Processor Clock Logic Block Diagram

##

Clock Generator Specification for AMD64 Processors

# Chapter 5 Pin Locations and Descriptions

Table 3 contains the pin descriptions for the Clock Generator.

Table 3. Pin Locations and Descriptions

| Name            | Pin                              | No. of<br>Pins | Туре | Pin Description                                                                                                                                                                                                                                                                                                       |

|-----------------|----------------------------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X1              | 3                                | 1              | I    | <b>Crystal Connection or External Reference:</b><br>Reference crystal input or external reference clock<br>input. This pin should include an internal 36-pF load<br>capacitance to eliminate the need for external load<br>capacitance.                                                                               |

| X2              | 4                                | 1              | 0    | <b>Crystal Connection:</b> Reference crystal feedback.<br>This output should include an internal 36-pF load<br>capacitance to eliminate the need for external load<br>capacitance.                                                                                                                                    |

| CPUT[1:0]       | 41<br>37                         | 2              | 0    | <b>Processor Clock Outputs 1 and 0:</b> Processor push-pull "True" clock outputs of the differential pair. Requires external termination.                                                                                                                                                                             |

| CPUC[1:0]       | 40<br>36                         | 2              | 0    | <b>Processor Clock Outputs 1 and 0:</b> Processor<br>push-pull "Complimentary" clock outputs of the<br>differential pair. Requires external termination.                                                                                                                                                              |

| PCI33_F         | 23                               | 1              | 0    | <b>3.3V Free-Running PCI Clock Output:</b> The free-running PCI clock pin operates at 33-MHz. The free-running PCI clock is not turned off when PCISTOP33_L is activated Low.                                                                                                                                         |

| PCI33[5:0]      | 13<br>14<br>17<br>18<br>21<br>22 | 6              | 0    | <b>3.3V PCI Clock Outputs:</b> PCI clocks operate at 33 MHz.                                                                                                                                                                                                                                                          |

| PCI33_HT66[2:0] | 7<br>8<br>11                     | 3              | 0    | <b>3.3V PCI 33 MHz or HyperTransport<sup>™</sup> Link</b><br><b>66 MHz Outputs:</b> This group of outputs is selectable<br>between 33 MHz and 66 MHz based upon the state of<br>PCI33_HT66SEL_L. When running 66 MHz, these<br>outputs are for use as reference clocks to<br>HyperTransport technology-based devices. |

24707 Rev. 3.08 September 2003

| Name                    | Pin           | No. of<br>Pins | Туре | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------|---------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI33_HT66SEL_L         | 6             | 1              | Ι    | PCI33_HT66 MHz Select: This input selects the<br>output frequency of PCI33_HT66 outputs to either 33<br>MHz or 66 MHz. This input pin is dedicated to avoid<br>corruption of the input state due to PCI add-in cards<br>that may have termination resistors on the input<br>clocks. This input must have a weak (100K) internal<br>pullup resistor. This pin externally strapped low using<br>a 10 K ohm resistor to select if the 66 Mhz outputs are<br>desired. Low = 66 MHz outputs, High = 33 MHz<br>outputs                                                                                                                                                            |

| USB                     | 31            | 1              | 0    | <b>3.3-V USB Clock Output:</b> Fixed clock output at 48-MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 24_48MHz/24<br>_48SEL_L | 28            | 1              | I/O  | <b>3.3-V Super I/O clock output:</b> The Super I/O clock<br>may be strapped for 24-MHz or 48-MHz. This input<br>must have a weak (100K) internal pullup. This pin<br>will be externally strapped low using a 10 K ohm if<br>the 48 MHz output is desired. Low = 48 MHz output,<br>high = 24 MHz output                                                                                                                                                                                                                                                                                                                                                                      |

| REF[0:2]/FS[0:2]        | 1<br>45<br>48 | 3              | I/O  | <ul> <li><b>3.3V Reference Clock Outputs:</b> Fixed clock output at 14.318 MHz.</li> <li><b>Frequency Select Inputs:</b> Power-On strapping to set device operating frequency as described in Table 2 on page 11. These inputs must have weak (100 K) internal pullup resistors. See Notes in Table 2 on page 11 for resistor strapping recommendation.</li> </ul>                                                                                                                                                                                                                                                                                                          |

| SPREAD                  | 44            | 1              | Ι    | <b>Spread Spectrum Clocking Enable:</b> Power-On<br>strapping that sets spread spectrum clocking as<br>enabled or disabled. This input allows the default<br>spread spectrum-clocking mode to be enabled or<br>disabled upon power up. This input must have a weak<br>(100K) internal pullup resistor. This pin is externally<br>strapped low using a 10 K ohm resistor if spread<br>disabled is desired. Low=disable, High=enable.<br>Note: all AMD Athlon <sup>™</sup> processors and<br>AMD64 processor-based systems are<br>recommended for use with SSC, therefore the<br>default of this pin is enabled and should only be<br>turned off for debug and test purposes. |

Table 3. Pin Locations and Descriptions (Continued)

| Name        | Pin                                        | No. of<br>Pins | Туре | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|--------------------------------------------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCISTOP33_L | 24                                         | 1              | Ι    | <b>Control for PCI33[0:5] and PCI33_HT66[0:2]</b><br><b>outputs operating at 33-MHz:</b> Active-Low control<br>input to halt all 33-MHz PCI clocks except the free-<br>running clock. This input must have a weak internal<br>pullup resistor (100 K). Once this input has been<br>asserted, the PCI33 outputs and PCI33_HT66 outputs<br>operating at 33MHz must stop in the Low state<br>according to the timing diagram outlined in Section<br>1.6.2 on page 7 and must not violate the output duty<br>cycle requirements until stopped (no glitches or runt<br>cycles). <b>Low = stop, High = running.</b> |

| NC          | 12                                         | 1              |      | Pin reserved for vendor specific features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SDATA       | 26                                         | 1              | I/O  | Data pin for I <sup>2</sup> C circuitry (SM Bus Rev1.0). This<br>input should have weak internal pullup resistor (100<br>K). In this case, no external pullup resistors would be<br>required. SDATA is a 5.0-V tolerant I/O.<br><i>Note Option: If CLK vendor only supports 3.3-V</i><br><i>tolerant I/O, they must provide an application</i><br><i>note in their spec on how to handle a 5V SMBus</i><br><i>(i.e., clamp circuit on the motherboard).</i>                                                                                                                                                   |

| SCLK        | 25                                         | 1              | Ι    | Clock pin for I <sup>2</sup> C circuitry (SM Bus Rev1.0). This<br>input must have weak internal pullup resistors (100K).<br>In this case, no external pullup resistors would be<br>required. SCLK must be a 3.3-V signal-tolerant I/O<br>but not 5.0-V tolerant                                                                                                                                                                                                                                                                                                                                               |

| VDD         | 2<br>9<br>16<br>19<br>29<br>35<br>38<br>46 | 8              | р    | <b>Power Connection:</b> Connected to 3.3 V power supply. Used to supply digital portions of the chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

24707 Rev. 3.08 September 2003

| Name | Pin                                               | No. of<br>Pins | Туре | Pin Description                                                                                                                            |

|------|---------------------------------------------------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| GND  | 5<br>10<br>15<br>20<br>27<br>30<br>34<br>39<br>47 | 9              | G    | <b>Power Connection:</b> Connected directly to GND on the motherboard. Used to ground digital portions of the chip.                        |

| VDDA | 43                                                | 1              | Р    | <b>Analog VDD:</b> Connected to 3.3-V power supply through a filter on the motherboard. Used to supply the main PLL on the chip.           |

| GNDA | 42                                                | 1              | G    | <b>Analog GND:</b> Connected directly to GND on the motherboard. Used to ground the main PLL on the chip.                                  |

| VDDF | 32                                                | 1              | Р    | Analog VDD for 48-MHz PLL: Connected to 3.3-V power supply through a filter on the motherboard. Used to supply the 48-MHz PLL on the chip. |

| GNDF | 33                                                | 1              | G    | Analog GND for 48-MHz PLL: Connected directly to GND on the motherboard. Used to ground the 48-MHz PLL on the chip.                        |

#### Table 3. Pin Locations and Descriptions (Continued)

# Chapter 6 Package Pinout – 48-Pin SSOP

The package pinout for a 48-pin SSOP package is defined to maximize performance. The package pinout provides grouped VDD and GND pin pairs to maximize mutual coupling and to equalize the distribution losses to each rail as seen at each signal location. The pinout includes dedicated VDDA and GNDA signals to supply the variable PLL and VDDF and GNDF signals to supply the fixed PLL. Figure 3 illustrates the SSOP package pinout.

Figure 3. SSOP Package Pinout

##

Clock Generator Specification for AMD64 Processors

# Chapter 7 Electrical Specifications

This chapter contains the electrical specifications for the clock generator.

## 7.1 Absolute Maximum Ratings

The absolute maximum ratings define the maximum non-operating conditions beyond which predictable operation of the device might be impaired. The device should not be subjected to conditions outside these ranges under any circumstances.

Table 4 describes the absolute maximum voltage, temperature, and ESD rating for the part.

| Parameter        | Description                                       | Rating      | Unit |

|------------------|---------------------------------------------------|-------------|------|

| VDD, VDDA, VDDF  | Supply Voltage                                    | -0.5 to 3.8 | V    |

| V <sub>IN</sub>  | Input Voltage                                     | -0.5 to 3.8 | V    |

| T <sub>STG</sub> | Storage Temp                                      | -65 to +150 | °C   |

| ESD PROT         | Input ESD Protection<br>using Human Body<br>Model | >2          | kV   |

#### **Table 4. Absolute Maximum Ratings**

## 7.2 **Operating Conditions**

Table 5 describes the normal operating conditions of the part.

#### **Table 5. Operating Conditions**

| Parameter            | Description                            | Min.  | Typical | Max.  | Unit |

|----------------------|----------------------------------------|-------|---------|-------|------|

| VDD, VDDA, VDDF      | Analog and digital supply voltages     | 3.135 |         | 3.465 | V    |

| T <sub>A</sub>       | Operating temperature, ambient         | 0     |         | 70    | °C   |

| F <sub>(Input)</sub> | Input frequency (crystal or reference) | 10    | 14.318  | 16    | MHz  |

# 7.3 Electrical Characteristics

The electrical characteristics of the device define the electrical parameters and the ranges over which the device must operate. These characteristics are grouped per input or output type. These electrical characteristics must be maintained over the operating conditions shown in Table 5 on page 25.

### 7.3.1 Logic Inputs

The logic input electrical characteristics are described in Table 6.

The input pins are PCI33\_HT66SEL\_L, FS[0:2], PCISTOP33\_L.

**Table 6. Logic Input Electrical Characteristics**

| Parameter       | Description               | Test Conditions                                       | Min.    | Тур. | Max.    | Unit |

|-----------------|---------------------------|-------------------------------------------------------|---------|------|---------|------|

| V <sub>IL</sub> | Input Low Voltage         | _                                                     | GND-0.3 | _    | 0.8     | V    |

| V <sub>IH</sub> | Input High Voltage        | _                                                     | 2.0     | _    | VDD+0.3 | V    |

| $I_{IL,}I_{IH}$ | Input Low/High<br>Current | 0 <vin< v<sub="">DD, Input<br/>Leakage current</vin<> | —       | _    | ±50     | μΑ   |

### 7.3.2 SDATA, SCLK Input/Output

The SMBus electrical characteristics are described in Table 7.

Table 7. SDATA and SCLK Input Electrical Characteristics \*

| Parameter       | Description               | Test Conditions                                     | Min.           | Тур.      | Max.           | Unit  |

|-----------------|---------------------------|-----------------------------------------------------|----------------|-----------|----------------|-------|

| V <sub>IL</sub> | Input Low Voltage         | -                                                   | GND-0.3        | _         | 0.8            | V     |

| V <sub>IH</sub> | Input High Voltage        | -                                                   | 2.0            | _         | VDD+0.3        | V     |

| $I_{IL,}I_{IH}$ | Input Low/High<br>Current | 0 <vin< vdd,<br="">Input Leakage<br/>current</vin<> | _              | _         | ±50            | μA    |

| V <sub>OL</sub> | Output Low Voltage        | $I_{OL} = 1.75 mA$                                  | GND-0.3        | _         | 0.4            | V     |

| I <sub>OL</sub> | Output Low Current        | $V_0 = 0.8V$                                        | 2              | _         | 50             | mA    |

| * Note: (5_V    | tolerant) If clock vendo  | r only supports 3 3-V to                            | lerant IO they | must nrov | ide an annlice | ition |

\* Note: (5-V tolerant) If clock vendor only supports 3.3-V tolerant IO, they must provide an application note in their specification on how to handle a 5-V SMBus (i.e., clamp circuit on the motherboard).

### 7.3.3 X1, X2 Crystal Input/Feedback

The crystal input electrical characteristics are described in Table 8.

#### **Table 8. Crystal Input/Feedback Electrical Characteristics**

| Parameter | Description                  | <b>Test Conditions</b> | Min. | Тур. | Max. | Unit |

|-----------|------------------------------|------------------------|------|------|------|------|

| Cinx      | Crystal pin load capacitance | —                      | 27   | 36   | 45   | pF   |

### 7.3.4 PCI/ HyperTransport<sup>TM</sup> Clock Outputs

The following PCI and HyperTransport<sup>™</sup> clock output electrical characteristics are described in Table 9.

The PCI and HyperTransport pins are PCI33[0:5], PCI\_F, PCI33\_HT66[0:2].

#### Table 9. PCI/HyperTransport<sup>™</sup> Clock Output Electrical Characteristics (Lump Capacitance Test Load =30 pF)

|    |                 |                          |                                                    | PCI33, PCI33_HT66<br>= 33MHz |       |     | 33_HT<br>66MHz |            |     |      |

|----|-----------------|--------------------------|----------------------------------------------------|------------------------------|-------|-----|----------------|------------|-----|------|

|    | Parameter       | Description              | <b>Test Conditions</b>                             | Min                          | Тур   | Max | Min            | Тур        | Max | Unit |

|    | V <sub>OL</sub> | Output Low<br>Voltage    | $I_{OL} = 9.0 \text{mA}$                           | —                            | Ι     | 0.4 | _              | -          | 0.4 | V    |

|    | $V_{OH}$        | Output High<br>Voltage   | $I_{OH} = -12mA$                                   | 2.4                          |       | 1   | 2.4            | -          | Ι   | V    |

| DC | I <sub>OL</sub> | Output Low<br>Current    | $V_0 = 0.8V$                                       | 10                           | _     | Ι   | 10             |            | Ι   | mA   |

|    | I <sub>OH</sub> | Output High<br>Current   | $V_0 = 2.0 V$                                      | -15                          | _     | Ι   | -15            |            | Ι   | mA   |

|    | f               | Frequency,<br>Actual     | _                                                  | _                            | 33.33 |     | Ι              | 66.6<br>67 |     | MHz  |

|    | t <sub>R</sub>  | Output Rise<br>Edge Rate | Measured from 20% to 60%                           | 1                            | l     | 4   | 1              | _          | 4   | V/ns |

| AC | $t_{\rm F}$     | Output Fall<br>Edge Rate | Measured from 60% to 20%                           | 1                            | -     | 4   | 1              | -          | 4   | V/ns |

|    | t <sub>D</sub>  | Duty Cycle               | Measured on rising<br>and falling edge at<br>1.5 V | 45                           | -     | 55  | 45             | _          | 55  | %    |

24707 Rev. 3.08 September 2003

|    |                 |                                                             |                                                                                                                                                                                                   | PCI.  | PCI33,<br>33_HT<br>33MHz |      | PCI33_HT6<br>66MHz |     | 66 = |      |

|----|-----------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------|------|--------------------|-----|------|------|

|    | Parameter       | Description                                                 | <b>Test Conditions</b>                                                                                                                                                                            | Min   | Тур                      | Max  | Min                | Тур | Max  | Unit |

|    | t <sub>JC</sub> | Jitter, Cycle-<br>to-Cycle                                  | Measured on rising<br>edge at 1.5V.<br>Maximum difference<br>of cycle time between<br>two adjacent cycles.                                                                                        | 0     | _                        | 250  | 0                  | _   | 250  | ps   |

| AC | t <sub>JA</sub> | Jitter,<br>Accumulated                                      | Measured using the<br>JIT2 software package<br>with a Tek 7404<br>scope.<br>TIE (Time Interval<br>Error) measurement<br>technique:<br>Sample resolution =<br>50 ps,<br>Sample Duration = 10<br>µs | -1000 | _                        | 1000 | -1000              |     | 1000 | ps   |

|    | $t_{\rm FS}$    | Frequency<br>Stabilization<br>from Power-up<br>(cold start) | Measured from full supply voltage.                                                                                                                                                                | 0     | _                        | 3    | 0                  | _   | 3    | mS   |

|    | R <sub>ON</sub> | Output<br>Impedance                                         | Average value during<br>switching transition.<br>Used for determining<br>series termination<br>value.                                                                                             | 12    | 15                       | 55   | 12                 | 15  | 55   | Ω    |

#### Table 9. PCI/HyperTransport<sup>™</sup> Clock Output Electrical Characteristics (Lump Capacitance Test Load =30 pF) (Continued)

### 7.3.5 **REF[2:0]** Clock Outputs

The Reference clock output electrical characteristics are described in Table 10.

Table 10. Reference Clock Output Electrical Characteristics

(Lump Capacitance Test Load = 20 pF)

|    | Parameter       | Description                                                 | Test Conditions                                                                                                                                                                    | Min   | Тур    | Max  | Unit |

|----|-----------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|------|------|

|    | V <sub>OL</sub> | Output Low<br>Voltage                                       | $I_{OL} = 9mA$                                                                                                                                                                     | _     | _      | 0.4  | V    |

| DC | $V_{OH}$        | Output High<br>Voltage                                      | $I_{OH}$ = -12mA                                                                                                                                                                   | 2.4   | —      | _    | V    |

| D  | I <sub>OL</sub> | Output Low<br>Current                                       | $V_0 = 0.8V$                                                                                                                                                                       | 16    | _      | _    | mA   |

|    | I <sub>OH</sub> | Output High<br>Current                                      | $V_0 = 2.0 V$                                                                                                                                                                      | -22   | _      | _    | mA   |

|    | f               | Frequency, Actual                                           | Frequency generated by crystal oscillator                                                                                                                                          |       | 14.318 |      | MHz  |

|    | t <sub>R</sub>  | Output Rise Edge<br>Rate                                    | Measured from 20% to 80%                                                                                                                                                           | 0.5   | _      | 2    | V/ns |

|    | $t_{\rm F}$     | Output Fall Edge<br>Rate                                    | Measured from 80% to 20%                                                                                                                                                           | 0.5   | _      | 2    | V/ns |

|    | t <sub>D</sub>  | Duty Cycle                                                  | Measured on rising and falling edge at 1.5V                                                                                                                                        | 45    | _      | 55   | %    |

|    | $t_{\rm JC}$    | Jitter, Cycle-to-<br>Cycle                                  | Measured on rising edge at 1.5V.<br>Maximum difference of cycle time<br>between two adjacent cycles.                                                                               | 0     | 500    | 1000 | ps   |

| AC | $t_{\rm JA}$    | Jitter,<br>Accumulated                                      | Measured using the JIT2 software<br>package with a Tek 7404 scope.<br>TIE (Time Interval Error)<br>measurement technique:<br>Sample resolution = 50 ps,<br>Sample Duration = 10 µs | -1000 | _      | 1000 | ps   |

|    | t <sub>FS</sub> | Frequency<br>Stabilization from<br>Power-up (cold<br>start) | Measured from full supply voltage.                                                                                                                                                 | 0     | _      | 3    | ms   |

|    | R <sub>ON</sub> | Output Impedance                                            | Average value during switching<br>transition. Used for determining<br>series termination value.                                                                                    | 20    | 24     | 60   | Ω    |

### 7.3.6 USB, 24\_48MHz Clock Outputs

The USB and 24\_48MHz clock output electrical characteristics are described in Table 11.

#### Table 11. 24\_48 MHz, USB Clock Output Electrical Characteristics (Lump Capacitance Test Load = 20 pF)

|    |                 |                                                                         |                                                                                                            | 24                           | 48MI | Iz     | USB | , 24_48 | MHz     |      |

|----|-----------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------|------|--------|-----|---------|---------|------|

|    | Parameter       | Description                                                             | Test Conditions                                                                                            | Min                          | Тур  | Max    | Min | Тур     | Ma<br>x | Unit |

| 0  | V <sub>OL</sub> | Output Low<br>Voltage                                                   | $I_{OL} = 9mA$                                                                                             | _                            |      | 0.4    | _   |         | 0.4     | V    |

|    | V <sub>OH</sub> | Output High<br>Voltage                                                  | $I_{OH}$ = -12mA                                                                                           | 2.4                          |      | —      | 2.4 |         | -       | V    |

| DC | I <sub>OL</sub> | Output Low<br>Current                                                   | $V_{OL} = 0.8 V$                                                                                           | 16                           |      | Ι      | 16  |         |         | mA   |

|    | I <sub>OH</sub> | Output High<br>Current                                                  | $V_{OL}=2.0V$                                                                                              | V <sub>OL</sub> = 2.0V -22 - |      | -22    |     |         | mA      |      |

|    | f               | Frequency,<br>Actual                                                    | Determined by PLL divider ratio                                                                            | 24.004                       |      | 48.008 |     |         | MHz     |      |

|    | t <sub>R</sub>  | Output Rise<br>Edge Rate                                                | Measured from 20% to 80%                                                                                   | rom 20% 0.5 2                |      | 2      | 0.5 |         | 2       | V/ns |

|    | t <sub>F</sub>  | Output Fall<br>Edge Rate                                                | Measured from 80% to 20%                                                                                   | 0.5                          |      | 2      | 0.5 |         | 2       | V/ns |

| 5) | t <sub>D</sub>  | Duty Cycle                                                              | Measured on rising<br>and falling edge at<br>1.5V                                                          | 45                           |      | 55     | 45  |         | 55      | %    |

| AC | t <sub>JC</sub> | Jitter, Cycle-<br>to-Cycle for<br>24_48MHz<br>clock                     | Measured on rising<br>edge at 1.5V.<br>Maximum difference<br>of cycle time between<br>two adjacent cycles. | 0                            | 250  | 500    | 0   | 250     | 500     | ps   |

|    | t <sub>JC</sub> | Jitter, Cycle-<br>to-Cycle for<br>USB clock<br>(required for<br>USB2.0) | Measured on rising<br>edge at 1.5V.<br>Maximum difference<br>of cycle time between<br>two adjacent cycles. |                              |      |        | 0   |         | 200     | ps   |

|    |                 |                                                                 |                                                                                                       | 24_48 MHz USB, 24_48 MHz |     |      |       | ИНz |          |      |

|----|-----------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------|-----|------|-------|-----|----------|------|

|    | Parameter       | Description                                                     | Test Conditions                                                                                       | Min                      | Тур | Max  | Min   | Тур | Ma<br>x  | Unit |

|    | t <sub>JA</sub> | Jitter,<br>Accumulated                                          | Measured using the<br>JIT2 software<br>package with a Tek<br>7404 scope.                              | -1000                    |     | 1000 | -1000 |     | 100<br>0 | ps   |

|    |                 |                                                                 | TIE (Time Interval<br>Error) measurement<br>technique:                                                |                          |     |      |       |     |          |      |

| AC |                 |                                                                 | Sample resolution = 50 ps,                                                                            |                          |     |      |       |     |          |      |

|    |                 |                                                                 | Sample Duration = 10 µs                                                                               |                          |     |      |       |     |          |      |

|    | t <sub>FS</sub> | Frequency<br>Stabilization<br>from Power-<br>up (cold<br>start) | Measured from full supply voltage                                                                     | 0                        |     | 3    | 0     |     | 3        | Ms   |

|    | R <sub>ON</sub> | Output<br>Impedance                                             | Average value during<br>switching transition.<br>Used for determining<br>series termination<br>value. | 20                       | 24  | 60   | 20    | 24  | 60       | Ω    |

#### Table 11. 24\_48MHz, USB Clock Output Electrical Characteristics (Lump Capacitance Test Load = 20 pF) (Continued)

### 7.3.7 CPUT[1:0], CPUC[1:0] Clock Outputs

The processor clock output electrical characteristics are described in Table 12.

|    | Parameter         | Description                                 | Test Conditions                                                                                                     | Min  | Тур  | Max  | Unit |

|----|-------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| AC | t <sub>R</sub>    | Rise Edge Rate                              | Measured at the AMD64 processors<br>test load. 0V± 400mV (differential<br>measurement)                              | 2    | _    | 10   | V/ns |

|    | t <sub>F</sub>    | Fall Edge Rate                              | Measured at the AMD64 processors<br>test load $0V \pm 400mV$ (differential<br>measurement)                          | 2    | _    | 10   | V/ns |

|    | V <sub>DIFF</sub> | Differential Voltage<br>(Single ended)      | Measured at the AMD64 processors<br>test load<br>(single-ended measurement)                                         | 0.40 | 1.25 | 2.3  | V    |

|    | $\Delta V_{DIFF}$ | Change in V <sub>DIFF_DC</sub><br>Magnitude | Measured at the AMD64 processors<br>test load<br>(single-ended measurement)                                         | -150 | _    | +150 | mV   |

| AC | V <sub>CM</sub>   | Common Mode<br>Voltage (Note 1)             | Measured at the AMD64 processors<br>test load<br>(single-ended measurement)                                         | 1.05 | 1.25 | 1.45 | V    |

| A  | $\Delta V_{CM}$   | Change in Common<br>Mode Voltage            | Measured at the AMD64 processors<br>test load<br>(single-ended measurement)                                         | -200 | _    | +200 | mV   |

|    | t <sub>D</sub>    | Duty Cycle                                  | Measured at the differential crossing point                                                                         | 45   | 50   | 53   | %    |

|    | t <sub>JC</sub>   | Jitter, Cycle-to-Cycle                      | Measured at the differential<br>crossing point. Maximum<br>difference of cycle time between<br>two adjacent cycles. | 0    | 100  | 200  | ps   |

|    | Parameter       | Description                                              | Test Conditions                                                                                                                                                          | Min   | Тур | Max  | Unit |

|----|-----------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|------|

|    | t <sub>JA</sub> | Jitter, Accumulated                                      | Measured using the JIT2 software package with a Tek 7404 scope.                                                                                                          | -1000 |     | 1000 | ps   |

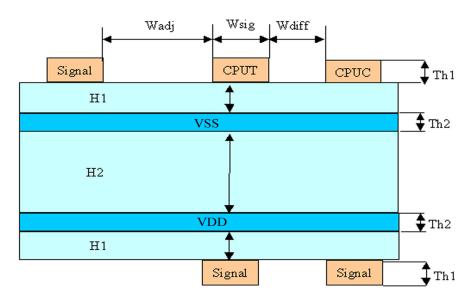

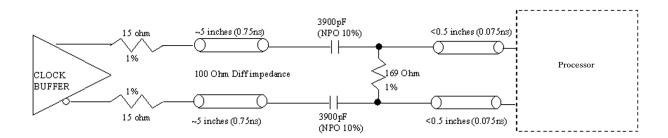

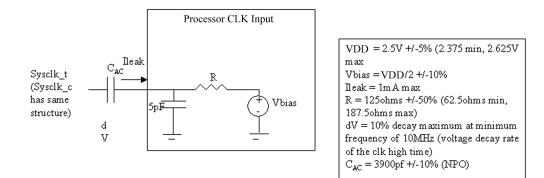

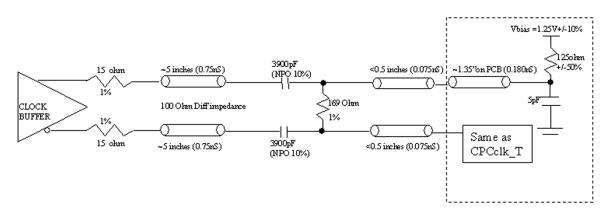

| AC |                 |                                                          | TIE (Time Interval Error)<br>measurement technique:                                                                                                                      |       |     |      |      |